吉林大學(xué)計(jì)算機(jī)系統(tǒng)結(jié)構(gòu)筆記 第三章 指令級(jí)并行(曲冠南老師版)與計(jì)算機(jī)系統(tǒng)集成服務(wù)

第三章 指令級(jí)并行(Instruction-Level Parallelism, ILP)筆記(曲冠南老師版)

一、 指令級(jí)并行概述

指令級(jí)并行(ILP)是指處理器通過在同一時(shí)間或重疊時(shí)間內(nèi)執(zhí)行多條指令(來自同一個(gè)程序序列)來提升性能的能力。它是現(xiàn)代高性能微處理器(如超標(biāo)量、超流水線處理器)的核心設(shè)計(jì)思想。目標(biāo)是挖掘程序指令流中潛在的并行性,以提高指令吞吐率(IPC,每時(shí)鐘周期指令數(shù))。

二、 實(shí)現(xiàn)ILP的關(guān)鍵技術(shù)與挑戰(zhàn)

1. 流水線基礎(chǔ)與冒險(xiǎn)(Hazards)

- 結(jié)構(gòu)冒險(xiǎn):硬件資源沖突。

- 數(shù)據(jù)冒險(xiǎn):數(shù)據(jù)依賴關(guān)系(RAW, WAR, WAW)。

- 控制冒險(xiǎn):由分支指令引起的流水線停頓。

2. 動(dòng)態(tài)調(diào)度技術(shù)

為了克服數(shù)據(jù)冒險(xiǎn),提高流水線利用率,現(xiàn)代處理器采用動(dòng)態(tài)調(diào)度:

- 記分板算法:早期的動(dòng)態(tài)調(diào)度方法,通過中央控制單元跟蹤指令狀態(tài)和資源,允許亂序執(zhí)行以解決數(shù)據(jù)冒險(xiǎn)。

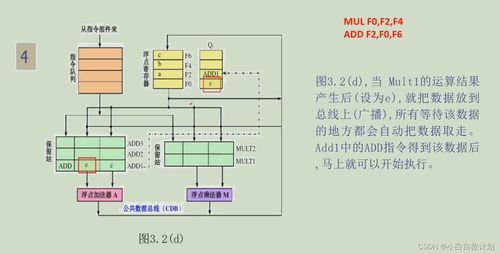

- Tomasulo算法:更先進(jìn)的動(dòng)態(tài)調(diào)度算法,核心思想包括:

- 寄存器重命名:使用保留站和ROB(Reorder Buffer)消除WAR和WAW冒險(xiǎn)。

- 分布式控制:功能單元保留站自主檢測(cè)操作數(shù)就緒情況。

- 公共數(shù)據(jù)總線(CDB):廣播結(jié)果,實(shí)現(xiàn)旁路(forwarding)。

3. 分支預(yù)測(cè)(Branch Prediction)

為減少控制冒險(xiǎn)帶來的性能損失:

- 靜態(tài)預(yù)測(cè):編譯器主導(dǎo)(如預(yù)測(cè)總是不跳轉(zhuǎn))。

- 動(dòng)態(tài)預(yù)測(cè):硬件根據(jù)運(yùn)行時(shí)歷史進(jìn)行預(yù)測(cè)。

- 分支歷史表(BHT):1位/2位飽和計(jì)數(shù)器。

- 分支目標(biāo)緩沖器(BTB):緩存跳轉(zhuǎn)目標(biāo)地址。

- 高級(jí)技術(shù):兩級(jí)自適應(yīng)預(yù)測(cè)器、錦標(biāo)賽預(yù)測(cè)器等。

4. 前瞻執(zhí)行(Speculative Execution)

結(jié)合動(dòng)態(tài)調(diào)度和分支預(yù)測(cè),在分支結(jié)果確認(rèn)前,前瞻地執(zhí)行預(yù)測(cè)路徑上的指令,結(jié)果暫存于ROB中。若預(yù)測(cè)正確則提交,錯(cuò)誤則清空流水線(沖刷),恢復(fù)現(xiàn)場(chǎng)。這是實(shí)現(xiàn)高性能ILP的關(guān)鍵。

5. 多發(fā)射處理器

- 超標(biāo)量(Superscalar):每個(gè)時(shí)鐘周期動(dòng)態(tài)發(fā)射多條指令(如2-8條),硬件負(fù)責(zé)調(diào)度。

- 超長(zhǎng)指令字(VLIW):編譯器將多條操作打包成一條長(zhǎng)指令,靜態(tài)調(diào)度,硬件簡(jiǎn)單。

- 對(duì)比:超標(biāo)量硬件復(fù)雜,但能適應(yīng)動(dòng)態(tài)情況;VLIW依賴于編譯器的強(qiáng)大能力,指令集與硬件綁定緊。

三、 限制ILP的因素

- 真實(shí)數(shù)據(jù)依賴(True Data Dependence):即RAW冒險(xiǎn),是程序的本質(zhì)屬性,無法消除。

- 過程(函數(shù))調(diào)用與返回。

- 分支預(yù)測(cè)的準(zhǔn)確性上限。

- 指令窗口和發(fā)射寬度的物理限制。

- 存儲(chǔ)器延遲與一致性:訪存延遲成為主要瓶頸。

- 復(fù)雜性增長(zhǎng):硬件設(shè)計(jì)復(fù)雜度(如調(diào)度邏輯、旁路網(wǎng)絡(luò))隨發(fā)射寬度呈平方甚至指數(shù)增長(zhǎng)。

四、 計(jì)算機(jī)系統(tǒng)集成服務(wù)(Computer System Integration Service)的聯(lián)系與思考

本章學(xué)習(xí)的指令級(jí)并行技術(shù),是構(gòu)建高性能計(jì)算系統(tǒng)硬件核心的理論與實(shí)踐基礎(chǔ)。而“計(jì)算機(jī)系統(tǒng)集成服務(wù)”則是將這些核心部件(如采用了先進(jìn)ILP技術(shù)的CPU、內(nèi)存、存儲(chǔ)、網(wǎng)絡(luò)等)以及軟件、網(wǎng)絡(luò)環(huán)境,根據(jù)用戶特定需求,進(jìn)行整體規(guī)劃、設(shè)計(jì)、組裝、調(diào)試和優(yōu)化的綜合性技術(shù)服務(wù)。

兩者關(guān)系體現(xiàn)在:

1. 技術(shù)選型依據(jù):系統(tǒng)集成工程師需要理解CPU的微架構(gòu)特性(如ILP實(shí)現(xiàn)程度、核心數(shù)、緩存層次),才能為客戶選擇匹配其應(yīng)用負(fù)載(如科學(xué)計(jì)算、數(shù)據(jù)庫(kù)、虛擬化)的服務(wù)器或工作站。例如,高ILP的CPU適合單線程性能要求高的應(yīng)用。

2. 性能調(diào)優(yōu)基礎(chǔ):在集成后的系統(tǒng)性能分析與優(yōu)化中,理解ILP有助于診斷“軟件瓶頸”。例如,當(dāng)CPU利用率高但吞吐量低時(shí),可能原因是程序分支過多導(dǎo)致預(yù)測(cè)失敗率高,或內(nèi)存訪問模式差導(dǎo)致流水線停頓,這需要從代碼或系統(tǒng)配置層面進(jìn)行優(yōu)化。

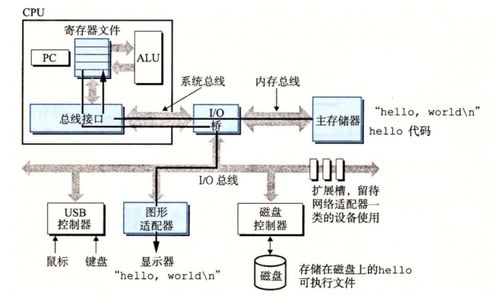

3. 系統(tǒng)平衡設(shè)計(jì):再?gòu)?qiáng)大的ILP能力也需要與快速的內(nèi)存子系統(tǒng)(低延遲、高帶寬)、高速I/O通道相匹配,否則會(huì)成為“無米之炊”。系統(tǒng)集成正是要確保各子系統(tǒng)協(xié)同無瓶頸。

4. 新興技術(shù)集成:隨著異構(gòu)計(jì)算(CPU+GPU/FPGA)和特定領(lǐng)域架構(gòu)(DSA)的興起,系統(tǒng)集成服務(wù)需要將擅長(zhǎng)控制流和ILP的通用CPU與擅長(zhǎng)數(shù)據(jù)級(jí)并行(DLP)的加速器集成,形成協(xié)同計(jì)算平臺(tái)。

****:

《計(jì)算機(jī)系統(tǒng)結(jié)構(gòu)》中指令級(jí)并行的深入學(xué)習(xí),為我們理解現(xiàn)代處理器的“心臟”如何工作提供了鑰匙。而“計(jì)算機(jī)系統(tǒng)集成服務(wù)”則是運(yùn)用這把鑰匙,結(jié)合對(duì)存儲(chǔ)、網(wǎng)絡(luò)、軟件等“全身器官”的理解,去構(gòu)建一個(gè)高效、穩(wěn)定、適用的完整“生命體”(計(jì)算系統(tǒng))。兩者是理論與應(yīng)用、微觀與宏觀的緊密結(jié)合,共同服務(wù)于最終的計(jì)算性能目標(biāo)。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://m.genzun.cn/product/81.html

更新時(shí)間:2026-04-14 04:00:51